## New Era of Panel Based Technology for Packaging, and Potential of Glass

#### Shin Takahashi

Technology Development General Division Electronics Company

# Connecting the World

#### Connecting the World

Smart Mobility

Green Energy /Environment BIG DATA

Smart Factory

Smart Mobile Devices Wearable Devices Wireless (5G)

# **AI & IOT & SENSORS**

Security/Biometrics

Medical

#### **Glass and Electronics**

| Designing<br>/Decorative<br>material | Opening<br>material<br>Laboratory<br>glass | Display<br>devices<br>Optical<br>component | Human<br>interface<br>devices |

|--------------------------------------|--------------------------------------------|--------------------------------------------|-------------------------------|

|                                      |                                            |                                            | <image/>                      |

0

## Glass Benefit for Semiconductor Packaging

High Resistivity and Electrically Low Insertion Loss

Glass Passive Device Source: STmicroelectronics

Transparency

Possibility of high volume and low cost based on panel size manufacturing

**Dimensional Stability**

Transceiver using TGV (Through Glass Vias) Source: Fraunhofer IZM, GIT2015

FOPLP using Glass Carrier Source: Sangyo Times

Demonstrator

ech

# Transition to Panel Level Manufacturing

# FOWLP/FOPLP

<u>TGV</u>

## FOWLP/PLP R&D activities around the world

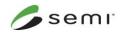

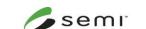

#### Fraunhofer IZM's PLP Consortium

Manufacturing line to transfer PLP technology to industry Focusing on Mold first approach

AGC

Datacon evo2200/ ASM Siplace CA3

Mahr OMS 600/ IMPEX proX3

WL: Towa up to 8" PL: APIC up to 18"x24" incl. 12" WL

Lauffer/

Bürkle

Siemens Microbeam/ Schmoll Picodrill with HYPER RAPID 50

Source: A\*STAR IME, Modified by AGC

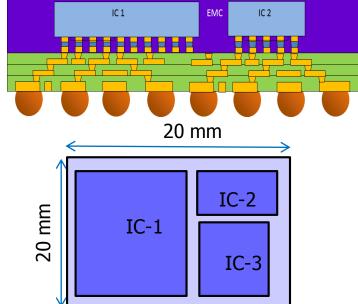

#### FOWLP/PLP R&D activities around the world

<u>A\*STAR IME's FOPLP Consortium</u>

Focusing on RDL first approach Plan to establish complete panel line by 2017

- Development of complete packaging process flow with Gen-3 panel

- Qualifying tools and materials for panel-base Fan-out multi-chip packaging

| Package Specifications for Phase-1 |                                           |  |

|------------------------------------|-------------------------------------------|--|

| Target App                         | Tablet, smart phones                      |  |

| Package                            | 20mm x20mm                                |  |

| Package<br>thickness               | 450um                                     |  |

| # of I/O                           | 2400                                      |  |

| # of chips/Pkg                     | 3                                         |  |

| Panel size                         | 550 mm x 650 mm                           |  |

| RDL L/S                            | 2 layers, (10/10, 5/5 um)                 |  |

| Benefits                           | Higher throughput $ ightarrow$ lower cost |  |

| Challenges                         | Handling large panel                      |  |

| Reliability                        | MSL3, TCOB 1000 cycles                    |  |

Note: \* Spec to be finalized with consortium members

AG

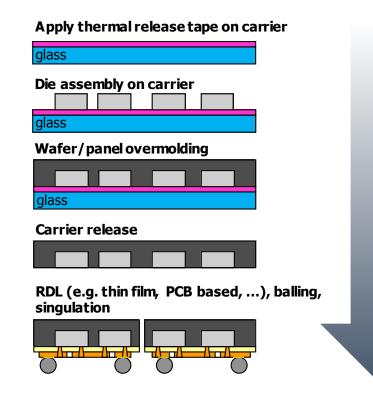

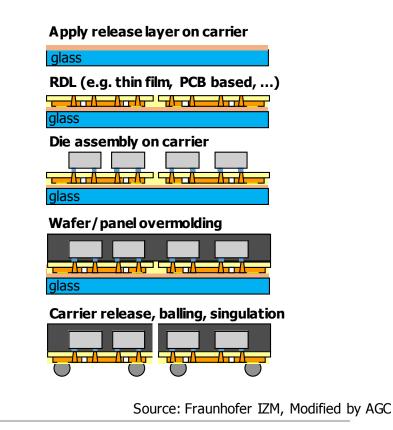

## Glass Carrier for FOWLP/PLP Manufacturing

#### Mold first

- Carrier for assembly and molding

- Temporary carrier for RDL processing (thin wafer handling, warpage compensation)

#### **RDL first**

Carrier for RDL build-up, assembly and molding

## Glass Lineup for FOWLP/FOPLP Carrier

|                | 3~4<br>ppm/C | 4~5<br>ppm/C | 5~6<br>ppm/C | 6~7<br>ppm/C | 7~8<br>ppm/C | 8~9<br>ppm/C | 9~10<br>ppm/C | 10~11<br>ppm/C | 11~12<br>ppm/C |

|----------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|----------------|----------------|

| Alkali<br>free |              |              |              |              |              |              |               |                |                |

| Alkali         |              |              |              |              |              |              |               |                |                |

#### Representative specification for 300mm glass carrier wafer

|         | Specification | Note              |

|---------|---------------|-------------------|

| TTV     | ≦5µm          | High spec: ≦1µm   |

| Ra      | ≦1.5nm        | High spec: ≦0.5nm |

| Warpage | ≦100µm        | High spec: ≦50µm  |

# FOWLP Assembly & Molding with Glass Carrier

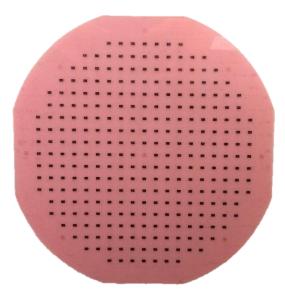

Assembled glass carrier with thermo-release tape

Compression molding of assembled glass carrier

Molded glass carrier before carrier release

Source: Fraunhofer IZM ,Modified by AGC

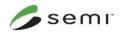

## Die Shift Test Result

Die Shift Factor Comparison on Wafer between Glass (6,8 ppm/K by AGC ) and Steel (12 ppm/K)

#### **Die Shift Factor:**

Linear displacement of dies after molding (CTE EMC =  $\sim$ 8 ppm/K)

- -> mainly due to CTE mismatch and chemical shrinkage of EMC.

- $\Rightarrow$  Die shift on the glass carrier is much lower than on the steel carrier.

#### **<u>Challenge: Robustness of glass carriers</u>**

AGC

🗾 Fraunhofer

Panel

Level Packaging

CONSORTIUN

IZM

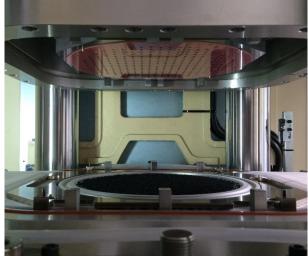

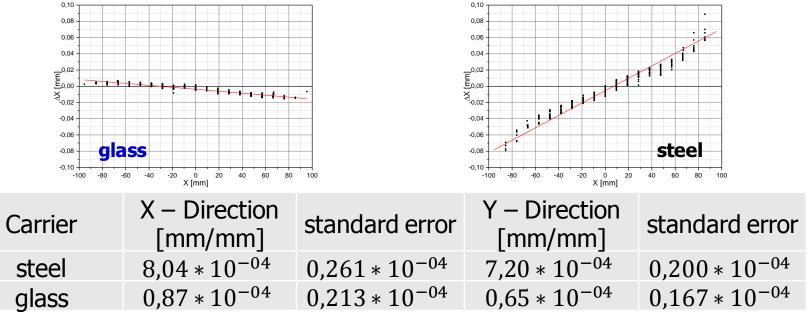

#### FOPLP Warpage Test Results

Panel size :  $660 \times 515 \text{ mm x 1 mmt}$ Die size :  $7.3 \times 7.3 \text{ mm}$  (945 pieces) Mold area :  $640 \times 495 \text{ mm x 0.4 mmt}$

- Die Mount @ Fuji Machine Mfg.

- Compression mold @ TOWA

- Carrier : Glass (AGC)

- Organic substrate (Hitachi Chemical)

Warpage: 15mm EMC: Film type (CTE: 8 ppm/C) Carrier: Organic substrate (CTE: 6 ppm/C)

Warpage: 3.0mm EMC: Film type (CTE: 7 ppm/C) Carrier: Glass (CTE: 9.6 ppm/C)

Warpage: -1.35mm EMC: Granule type (CTE: 7 ppm/C) Carrier: Glass (CTE: 8.3 ppm/C)

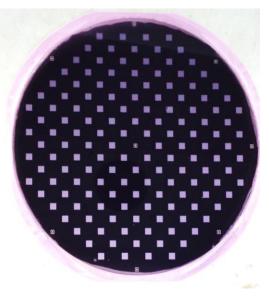

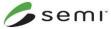

## Lab to Fab, TGV is getting to launch

## TGV is moving to panel size

|                             | Wafer                                                              | Panel                    |

|-----------------------------|--------------------------------------------------------------------|--------------------------|

|                             | 200mm dia.                                                         | 300mm x 400mm            |

| Size                        | 6inch, 8inch, 12inch                                               | ~550mm x 650mm (Gen-3)   |

| Thickness                   | 100~500um                                                          | 100~500um                |

| Representative<br>Hole Size | φ20~150um                                                          | φ65~150um                |

| Hole Pitch                  | Minimum 2x Hole Diameter                                           | Minimum 2x Hole Diameter |

| TGV<br>Metallization        | Cu conformal plating, Cu full-filled plating, and Cu paste filling | Cu conformal plating     |

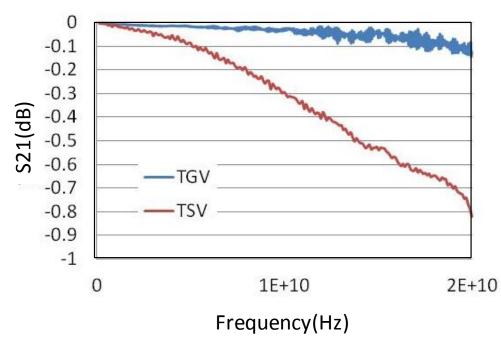

#### TGV contributes to miniaturized RF devices

Highly bulk resistance of TGV resulted in insertion loss less than -0.12dB at 20GHz.

Source: Dai Nippon Printing

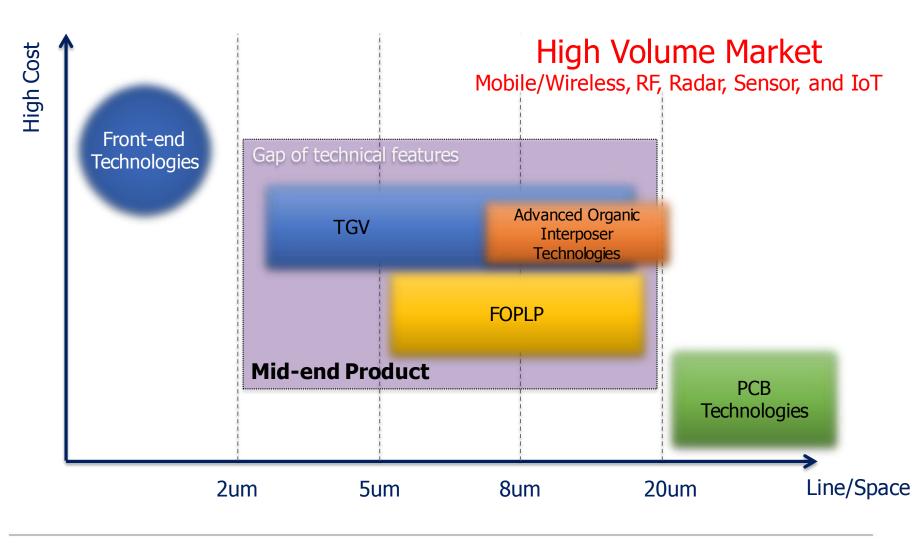

# Where Panel Technologies go

#### The necessity of panel technologies

#### Summary

- R&D consortium for FOPLP using large glass carrier is taking off. Glass panel is a good candidate as carrier material because of flat surface and an availability of different CTE.

- TGV is moving to panel size up to Gen-3 from wafer size. RF is a possible application based on better material properties (low insertion loss) of glass.

- Panel technologies will be an important to realize high volume manufacturing for mid-end products in a future connected world.

# "Look Beyond" Glass is only the Beginning. AGC